Hindawi Publishing Corporation Active and Passive Electronic Components Volume 2012, Article ID 729328, 6 pages doi:10.1155/2012/729328

# Research Article

# Gate Stack Engineering and Thermal Treatment on Electrical and Interfacial Properties of Ti/Pt/HfO<sub>2</sub>/InAs pMOS Capacitors

# Chung-Yen Chien, Jei-Wei Hsu, Pei-Chin Chiu, Jen-Inn Chyi, and Pei-Wen Li

Department of Electrical Engineering, National Central University, Chungli 32001, Taiwan

Correspondence should be addressed to Pei-Wen Li, pwli@ee.ncu.edu.tw

Received 16 March 2012; Revised 6 June 2012; Accepted 11 June 2012

Academic Editor: Yeong-Her Wang

Copyright © 2012 Chung-Yen Chien et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Effects of gate stack engineering and thermal treatment on electrical and interfacial properties of Ti/Pt/HfO<sub>2</sub>/InAs metal insulator semiconductor (MIS) capacitors were systematically evaluated in terms of transmission electron microscopy, energy dispersive X-ray spectroscopy, current-voltage, and capacitance-voltage characterizations. A 10 nm thick Pt metal effectively suppresses the formation of interfacial oxide, TiO<sub>2</sub>, between the Ti gate and HfO<sub>2</sub> gate dielectric layer, enhancing the gate modulation on the surface potential of InAs. An *in situ* HfO<sub>2</sub> deposition onto the *n*-InAs channel with an interfacial layer (IL) of one-monolayer InP followed by a 300°C post-metal-anneal produces a high-quality HfO<sub>2</sub>/InAs interface and thus unravels the annoying Fermi-level pinning, which is evidenced by the distinct capacitance dips in the high-/low-frequency *C-V* characteristics. The interface trap states could be further suppressed by replacing the InP IL by an As-rich InAs, which is substantiated by a gate leakage reduction and a steep voltage-dependent depletion capacitance.

### 1. Introduction

Motivation to study low band-gap InAs and InSb channels for next-generation metal oxide semiconductor (MOS) transistors is strong in light of their superior carrier mobility [1] and established epitaxy techniques [2, 3] among other emerging technologies such as carbon nanotube and graphite. However, the progress of realizing highperformance InAs and InSb MOS transistors has been impeded by the stringent restraint on thermal budget as well as the lack of robust gate dielectrics and suitable surface treatments for unraveling annoying Fermi-level pinning [4] at the oxide/semiconductor interface. Recently encouraging experimental demonstrations of high-K gate dielectrics (Gd<sub>2</sub>O<sub>3</sub>,  $Al_2O_3$ , and  $HfO_2$ ) on GaAs [5–7], InP [8], and InAs [9–11] channels using atomic-layer deposition (ALD) techniques have shed lights and attracted tremendous attentions on this venerable subject. In spite that various chemical and plasma surface treatments [12–14] have been proposed for annihilating surface states of III-V compound semiconductors, it still remains elusive how to produce a clean and well-passivated channel surface for subsequent high-quality gate dielectric growth. The most practical and promising approach for the surface preparation of III-V channels appears to be the *in situ* growth of gate dielectrics on channels.

In this paper, the authors report the interfacial and electrical properties of Ti/Pt/HfO<sub>2</sub>/InAs pMOS capacitors, in which a high-K gate dielectric, HfO<sub>2</sub> was grown on an n-InAs epitaxial layer without breaking vacuum by means of the integration of a molecular beam epitaxy system (Riber-32 MBE) with an atomic layer deposition system (Picoson R-100 ALD). In order to prevent thermal evaporation of InAs, all the device fabrication processes were kept below 300°C. Both Ti and Pt metals were evaluated for the gate materials. The interfacial layer effect arising from one-monolayer InP or As-rich InAs between HfO<sub>2</sub> and InAs channel, the deposition conditions of HfO<sub>2</sub>, and post-metal-anneal (PMA) processes were systematically studied for improving the interfacial and electrical properties of HfO<sub>2</sub>/InAs pMOS capacitors.

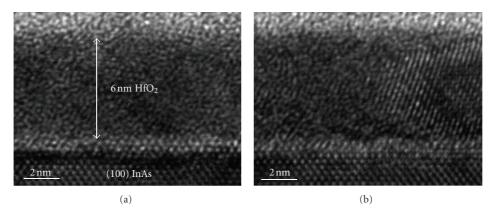

FIGURE 1: CTEM images of HfO<sub>2</sub> in situ deposited on InP/InAs channel at (a) 200°C and (b) 300°C. Abrupt and native oxide free interface provides a promising interface for MOS applications.

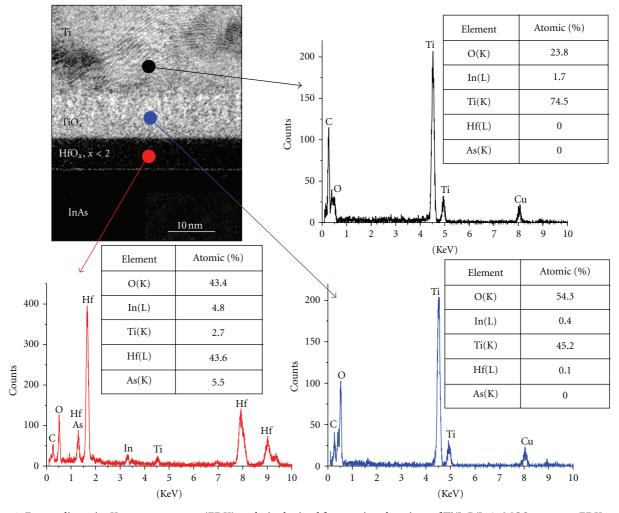

FIGURE 2: Energy dispersive X-ray spectroscopy (EDX) analysis obtained from various locations of Ti/InP/InAs MOS structure. EDX analysis reveals that an interfacial TiO $_x$  ( $x \sim 1.2$ ) and Hf-rich oxide were formed after Ti deposition onto HfO $_2$ /InP/InAs structure.

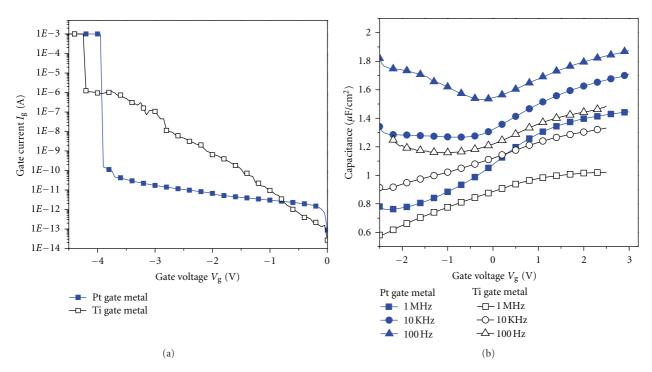

FIGURE 3: (a) I-V and (b) C-V characteristics of HfO<sub>2</sub>/InP/InAs MOS capacitors of  $100 \times 100 \,\mu\text{m}^2$  with Ti and Pt gate metal, respectively.

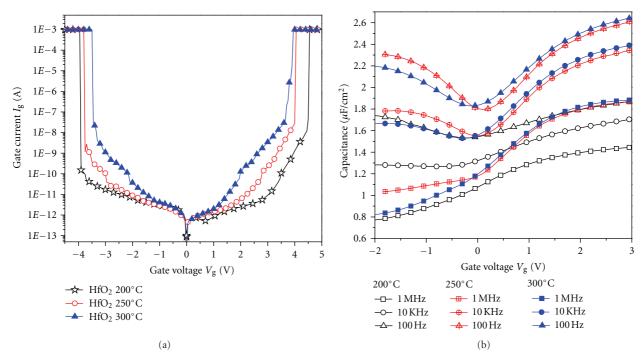

FIGURE 4: (a) *I-V* and (b) frequency-dependent *C-V* characteristics of Pt/HfO<sub>2</sub>/InP/InAs MOS capacitors in which HfO<sub>2</sub> was deposited at 200, 250, and 300°C, respectively.

# 2. Experimental

The fabrication of  $HfO_2/InAs$  MOS capacitors started with a 2" (100) n-InAs substrate doped with Si [(2–5)  $\times$  10<sup>17</sup> cm<sup>-3</sup>], followed by an epitaxial growth of a

200 nm thick n-InAs channel layer uniformly doped with Si in a concentration of 2  $\times$  10<sup>17</sup> cm<sup>-3</sup> and an one-monolayer InP or As-rich InAs IL on the top of InAs channel. After transferring the sample from the MBE growth chamber to ALD system through a high-vacuum

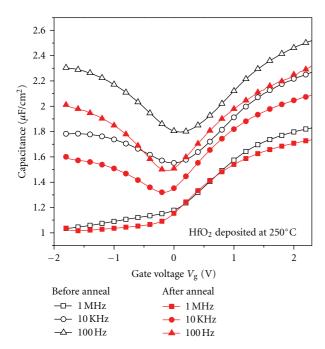

FIGURE 5: Frequency-dependent *C-V* characteristics of Pt/HfO<sub>2</sub>/InP/InAs MOS capacitors in which HfO<sub>2</sub> was deposited at 250°C before and after a subsequent 300°C forming gas PMA.

chamber with a base pressure of  $6 \times 10^{-8}$  Torr, a 6 nm thick HfO<sub>2</sub> layer was deposited at 200-300°C using water vapor and tetrakis(ethylmethylamino)hafnium [TEMAH,  $Hf[N(C_2H_5)(CH_3)]_4$  precursors. A 300 nm thick Ti or a 50 nm thick Pt was evaporated as gate materials followed by the gate definition either using photolithography and HF/H<sub>2</sub>O<sub>2</sub> chemical etching or through a shadow mask. Finally, the fabrication of MOS capacitors was completed by the evaporation of a 100 nm thick Al onto the substrate as the back-gate electrode and a 300°C PMA for 30 min. The interfacial and structural properties of the Ti/Pt/HfO2/InAs system were examined using high-resolution transmission electron microscopy (HRTEM) and energy dispersive Xray spectroscopy (EDX). The current-voltage (I-V) and capacitance-voltage (C-V) characteristics of the HfO<sub>2</sub>/InAs MOS capacitors were characterized using Keithley-4200 and HP4284 semiconductor analyzers.

#### 3. Results and Discussion

Figure 1 shows the cross-sectional TEM (CTEM) images of the gate stack of Ti/HfO<sub>2</sub>/InP/InAs structure. The *in situ* growth of HfO<sub>2</sub> on an InP/InAs channel produces a native-oxide free and abrupt HfO<sub>2</sub>/InP/InAs interface, indicating dangling bonds or surface states of InP/InAs are suppressed and providing a good interface for charge inversion under gate modulation. Additionally, there appears to be a 10–12 nm thick interfacial layer between a 6 nm thick HfO<sub>2</sub> layer and Ti-gate, and EDX analysis reveals that the chemical composition of the interfacial layer is  $\text{TiO}_x$  ( $x \sim 1.2$ ) and the underlay hafnium oxide becomes a Hf-rich oxide

(Figure 2), suggesting Ti catalytically releases oxygen from the stoichiometric  $HfO_2$ , forming a Hf-rich oxide, and the subsequent reaction of Ti and released oxygen generates  $TiO_x$ . The undesired interfacial  $TiO_x$  and Hf-rich oxide layers not only deteriorate the oxide integrity but also thicken the gate dielectrics thickness, which are evidenced by a high-gate leakage, a poor gate modulation on the surface potential of InAs channel but a slightly higher breakdown voltage as illustrated in the I-V and C-V characteristics (Figure 3).

An interesting finding that we have made through TEM observation is that a thin Pt barrier metal before Ti deposition effectively suppresses the formation of an interfacial oxide layer and retains the stoichiometry and high quality of  $HfO_2$ . The dielectric thickness of the Pt-gated MIS capacitor is 6 nm thick  $HfO_2$ , whereas the Ti-gated MIS capacitors have a gate oxide of 16-18 nm (10-12 nm  $TiO_x$  and 6 nm Hf-rich oxide). Although the thinner gate dielectric in the Pt-gated MIS capacitors sustains a smaller breakdown voltage than Ti-gated devices do, the reduction of gate leakage is more than 4 orders in magnitude as compared with the Ti-gated MIS capacitors. As a consequence, there appear a significant increase in the accumulation capacitance for a Pt-gated MIS diode and an enhanced gate modulation from C-V characteristics in Figure 3(b).

The gate-oxide integrity appears to be strongly dependent on the HfO2 deposition temperature and the thermal treatment after metal patterning. Increasing the deposition temperature from 200 to 250°C not only enhances the accumulation capacitance because of an increase in the dielectric constant of HfO<sub>2</sub> from 11 to 15, but also improves the inversion capacitance as a consequence of a better HfO<sub>2</sub>/InP/InAs interface. This is evidenced by a steep C-V transition in the depletion regime and a distinct capacitance dip when gate voltage modulates the surface potential of the InAs channel from depletion to inversion regimes (Figure 4). However, a higher HfO<sub>2</sub> deposition temperature at 300°C degrades the gate leakage and breakdown Efield accordingly, possibly originating from the crystallinity of HfO<sub>2</sub> transitioning from amorphous to polycrystalline phases from 200 to 300°C (Figure 1(b)). An additional 300°C PMA in H<sub>2</sub>/N<sub>2</sub> ambient for 30 min further appears to reduce the dangling-bonds and annihilates the surface states at the HfO<sub>2</sub>/InP/InAs interface, but also improves the frequencydependence of the accumulation capacitance as a result of the dielectric constant dispersion (Figure 5). The above mentioned experimental results also suggests that the InAs epitaxial layer is of high quality and does not degrade after a long duration (45 min) of 300°C ALD and PMA process.

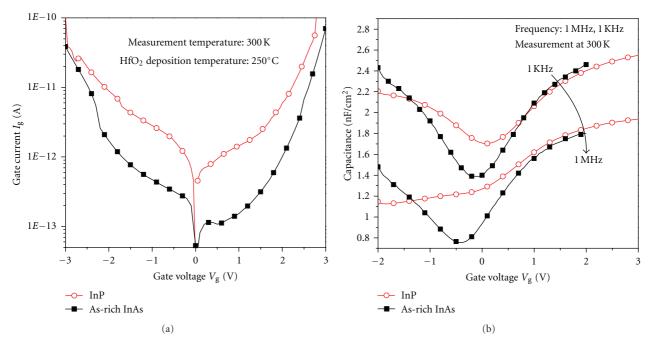

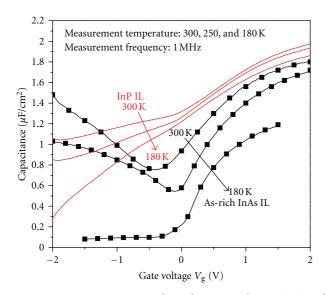

The interfacial properties and electrical characteristics of InAs MOS capacitors could be further improved by replacing the unrelaxed InP IL with a latticed match As-rich InAs IL, in spite that the bandgap of InAs (0.345 eV) is smaller than InP (1.344 eV). This is evidenced by a reduction of the gate leakage by one order in magnitude as shown in Figure 6(a). This is also substantiated by a steeper slope in the depletion region of the *C-V* characteristics in Figure 6(b). Suppressed surface states by As-rich IL and a high-thermal generation rate in narrow band-gap InAs [15] make the *C-V* curves

FIGURE 6: (a) I-V and (b) C-V characteristics of Pt/HfO<sub>2</sub>/InAs MOS capacitors with respective InP or As-rich InAs interfacial layers.

FIGURE 7: 1 MHz temperature-dependent *C-V* characteristics of InAs MOS capacitor with respective InP or As-rich interfacial layers.

measured at 1 MHz deviate from the conventional high-frequency C-V characteristics, in particular, at the inversion regime (Figure 7). For example, the inversion capacitances at 300 and 250 K are voltage dependent and getting close to the value of the gate oxide capacitance, instead of the effective capacitance of gate oxide capacitance in series with the depletion capacitance. Decreasing measurement temperature from 300 to 180 K decreases the thermal-generated carrier population and makes the inversion capacitance value restoring back to the one of typical high-frequency C-V characteristics. The extracted interface trap density  $(D_{\rm it})$

using a conductance method from the Pt/HfO<sub>2</sub>/InAs MOS capacitors with InP and As-rich interfacial layer is  $1.59 \times 10^{13}$  and  $7 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>, respectively, which are comparable with reported data [9–11].

#### 4. Conclusion

The *in situ* growth of  $HfO_2$  on InAs channel produces an abrupt and oxide-free interface, which is an important prerequisite for high-performance InAs MOS devices. The interfacial and electrical properties of  $HfO_2$ /InAs MOS capacitors are strongly influenced by the gate metal,  $HfO_2$  deposition temperature, the post-metal anneal, and interfacial control layer between  $HfO_2$  and InAs channel. A Pt barrier metal effectively suppresses the formation of interfacial  $TiO_x$  oxide and thus significantly improves the gate leakage and insulating quality of the gate stack. The gate oxide integrity and the gate dielectric constant of  $HfO_2$  could be further improved by a 250°C ALD deposition and a 300°C PMA treatment. An As-rich InAs IL further suppress surface states, evidenced by the reduction of gate leakage, and depletion/inversion capacitances.

## Acknowledgments

This work was supported by the National Science Council, Republic of China under Contract NSC 99-2622-E-008-017-CC1 and Joint Development Project (JDP) with Taiwan Semiconductor Manufacturing Company (TSMC). The authors would like to thank for the valuable discussions with Dr. Y. R. Lin, C. C. Cheng, C. H. Ko, and C. H. Wann from TSMC.

#### References

- G. Dewey, M. K. Hudait, K. Lee et al., "Carrier transport in high-mobility III-V quantum-well transistors and performance impact for high-speed low-power logic applications," *IEEE Electron Device Letters*, vol. 29, no. 10, pp. 1094–1097, 2008.

- [2] L. Goldstein, F. Glas, J. Y. Marzin, M. N. Charasse, and G. Le Roux, "Growth by molecular beam epitaxy and characterization of InAs/GaAs strained-layer superlattices," *Applied Physics Letters*, vol. 47, no. 10, pp. 1099–1101, 1985.

- [3] A. J. Noreika, M. H. Francombe, and C. E. C. Wood, "Growth of Sb and InSb by molecular-beam epitaxy," *Journal of Applied Physics*, vol. 52, no. 12, pp. 7416–7420, 1981.

- [4] H. S. Kim, I. Ok, M. Zhang et al., "A study of metal-oxide-semiconductor capacitors on GaAs, In<sub>0.53</sub> Ga<sub>0.47</sub>As, InAs, and InSb substrates using a germanium interfacial passivation layer," *Applied Physics Letters*, vol. 93, no. 6, Article ID 062111, 3 pages, 2008.

- [5] G. K. Dalapati, Y. Tong, W. Y. Loh, H. K. Mun, and B. J. Cho, "Impact of interfacial layer control using Gd<sub>2</sub> O<sub>3</sub> in HfO<sub>2</sub> gate dielectric on GaAs," *Applied Physics Letters*, vol. 90, no. 18, Article ID 183510, 3 pages, 2007.

- [6] H. C. Lin, T. Yang, H. Sharifi et al., "Enhancement-mode GaAs metal-oxide-semiconductor high-electron-mobility transistors with atomic layer deposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric," *Applied Physics Letters*, vol. 91, no. 21, Article ID 212101, 3 pages, 2007.

- [7] F. S. Aguirre-Tostado, M. Milojevic, K. J. Choi et al., "S passivation of GaAs and band bending reduction upon atomic layer deposition of HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanolaminates," *Applied Physics Letters*, vol. 93, no. 6, Article ID 061907, 3 pages, 2008.

- [8] Y. S. Kang, C. Y. Kim, M. H. Cho et al., "Thickness dependence on crystalline structure and interfacial reactions in HfO<sub>2</sub> films on InP (001) grown by atomic layer deposition," *Applied Physics Letters*, vol. 97, no. 17, Article ID 172108, 3 pages, 2010.

- [9] D. Wheeler, L.-E. Wernersson, L. Fröberg et al., "Deposition of HfO<sub>2</sub> on InAs by atomic-layer deposition," *Microelectronic Engineering*, vol. 86, no. 7-9, pp. 1561–1563, 2009.

- [10] J. Wu, E. Lind, R. Timm, M. Hjort, A. Mikkelsen, and L.-E. Wernersson, "Al<sub>2</sub>O<sub>3</sub>/InAs metal-oxide-semiconductor capacitors on (100) and (111)B substrates," *Applied Physics Letters*, vol. 100, no. 13, pp. 132905–132907, 2012.

- [11] H. D. Trinh, E. Y. Chang, Y. Y. Wong et al., "Effects of wet chemical and trimethyl aluminum treatments on the interface properties in atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> on InAs," *Japanese Journal of Applied Physics*, vol. 49, no. 11, Article ID 111201, 2010.

- [12] H. Oigawa, J. F. Fan, Y. Nannichi, H. Sugahara, and M. Oshima, "Universal passivation effect of (NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> treatment on the surface of III-V compound semiconductors," *Japanese Journal of Applied Physics*, vol. 30, no. 3, pp. L322–L325, 1991.

- [13] H. D. Trinh, E. Y. Chang, P. W. Wu et al., "The influences of surface treatment and gas annealing conditions on the inversion behaviors of the atomic-layer-deposition Al<sub>2</sub>O<sub>3</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitor," *Applied Physics Letters*, vol. 97, no. 4, Article ID 042903, 3 pages, 2010.

- [14] C. Marchiori, D. J. Webb, C. Rossel et al., "H plasma cleaning and a-Si passivation of GaAs for surface channel device applications," *Journal of Applied Physics*, vol. 106, no. 11, Article ID 114112, 8 pages, 2009.

- [15] P. D. Ye, "Main determinants for III-V metal-oxide-semiconductor field-effect transistors (invited)," *Journal of Vacuum Science and Technology A*, vol. 26, no. 4, pp. 697–704, 2008.

Submit your manuscripts at http://www.hindawi.com