Hindawi Publishing Corporation Active and Passive Electronic Components Volume 2015, Article ID 460416, 9 pages http://dx.doi.org/10.1155/2015/460416

### Research Article

# Usage and Limitation of Standard Mobility Models for TCAD Simulation of Nanoscaled FD-SOI MOSFETs

## A. Ciprut, A. Chelly, and A. Karsenty

<sup>1</sup>Faculty of Electrical and Computer Engineering, University of Rochester, NY 14627, USA

Correspondence should be addressed to A. Karsenty; karsenty@jct.ac.il

Received 4 March 2015; Revised 1 May 2015; Accepted 11 May 2015

Academic Editor: Gerard Ghibaudo

Copyright © 2015 A. Ciprut et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

TCAD tools have been largely improved in the last decades in order to support both process and device complementary simulations which are usually based on continuously developed models following the technology progress. In this paper, we compare between experimental and TCAD simulated results of two kinds of nanoscale devices: ultrathin body (UTB) and nanoscale Body (NSB) SOI-MOSFET devices, sharing the same W/L ratio but having a channel thickness ratio of 10:1 (46 nm and 4.6 nm, resp.). The experimental transfer I-V characteristics were found to be surprisingly different by several orders of magnitude. We analyzed this result by considering the severe mobility degradation and the influence of a large gate voltage dependent series resistance ( $R_{SD}$ ). TCAD tools do not usually consider  $R_{SD}$  to be either channel thickness or gate voltage dependent. After observing a clear discrepancy between the mobility values extracted from our measurements and those modeled by the available TCAD models, we propose a new semiempirical approach to model the transfer characteristics.

#### 1. Introduction

Nanoscale silicon-on-insulator (SOI) metal-oxide-semi-conductor field-effect transistor (MOSFET) based devices are the building blocks of up-to-date systems allowing ultrafast data processing. This is in accordance with efforts to develop new generation of ultrafast computers based on combined electronic and signal processing on one hand [1] and advanced generations of nanoscale devices (NSB) for communication systems [2] on the other hand. Furthermore, the excellent control of leakage current and short channel effects, achievable by means of UTB SOI-MOSFET architectures, makes them good candidates for ultimate nanometer scale. Consequently, the transport properties' study of thin semiconductor films has attracted considerable attention in the recent years.

In this perspective, the use of TCAD tools for predicting and optimizing such advanced semiconductor devices has increased recently [3, 4]. Since the nanotechnology's process and device evolution is quite rapid, there may appear some gaps among existing TCAD models. Indeed, TCAD tools use classic parametric models where some of them tend to become obsolete for nanoscale devices. For instance, it is well established that quantum effects and/or interface effects mainly govern the conduction of modern devices (e.g., ballistic transport effects or decreasing of the mobility by decreasing the channel thickness) [5]. Moreover, series resistance effects are of great importance for such devices and are the scope of intensive research activities [6–8] as well as the usage of the Y-function method in the last decades [9–12] to extract this parameter [13]. In this paper, we show how a semiempirical model based on gate voltage dependent series resistance established in a previous work [8] can be integrated in a TCAD simulator to match nonconventional electrical transfer characteristics of FD-SOI MOSFETs.

#### 2. TCAD Process Simulation

The layers deposition process was simulated by a commercial 3D TCAD process simulator (Csuprem from Crosslight) according to the process conditions used to fabricate

<sup>&</sup>lt;sup>2</sup>Faculty of Engineering, Bar-Ilan University, 52900 Ramat Gan, Israel

<sup>&</sup>lt;sup>3</sup>Faculty of Engineering, Department of Applied Physics, Jerusalem College of Technology, 91160 Jerusalem, Israel

| Layer # | Layer # Layer name Layer acron |        | Layer thickness [nm] | Function and properties                                                                                                                                                                                                        |  |  |  |  |

|---------|--------------------------------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 01      | Bulk silicon                   | Bulk   | 500,000              | Substrate p-type boron ( $10^{15}$ cm <sup>-3</sup> )<br>Resistivity: $14-22 \Omega \cdot \text{cm}$<br>Orientation $\langle 100 \rangle$                                                                                      |  |  |  |  |

| 02      | Buried oxide                   | ВОХ    | 70                   | Bulk insulator<br>O <sup>+</sup> implantation energy: 120 keV (2.35 hours)<br>Dose: 0.39 10 <sup>18</sup> O <sup>+</sup> cm <sup>-2</sup><br>Annealing: 1320°C (6.00 hours)                                                    |  |  |  |  |

| 03a     | Silicon-On-<br>Insulator       | SOI    | 46                   | p-type boron (10 <sup>15</sup> cm <sup>-3</sup> ) regular transistor channel in UTB do<br>and nonreduced SOI in GRC devices (source-drain extension                                                                            |  |  |  |  |

| 03b     | Gate-recessed silicon          | GRS    | 1.6–6.5 range        | Thinned transistor channel in GRC devices                                                                                                                                                                                      |  |  |  |  |

| 03c     | Pad oxide                      | PAD OX | 15                   | Relieve stress from silicon to nitride at high temperature                                                                                                                                                                     |  |  |  |  |

| 04      | Gate oxide                     | GOX    | 26                   | Gate insulator                                                                                                                                                                                                                 |  |  |  |  |

| 05      | Polysilicon                    | Poly   | 220                  | Gate electrode                                                                                                                                                                                                                 |  |  |  |  |

| 06      | Nitride 2                      | Nit    | 30                   | Prevent further oxidation of the thin silicon layer during the implant's thermal annealing (GRC)                                                                                                                               |  |  |  |  |

| 07      | Field oxide                    | FOX    | 700                  | Active area insulator                                                                                                                                                                                                          |  |  |  |  |

| 08      | Silox                          | SOX    | 350                  | Contact opening mask for source/drain and gate passivation                                                                                                                                                                     |  |  |  |  |

| 09      | Polysilicon                    | Poly   | 220                  | Source/drain poly contacts<br>Source/drain doping obtained by phosphorous implant:<br>dose D = $2.5 \cdot 10^{15}$ cm <sup>-2</sup> ,<br>energy E = $30$ keV,<br>HTA high temperature annealing T = $1000^{\circ}$ C, (30 min) |  |  |  |  |

| 10      | Aluminum                       | Al     | 500                  | Source/drain metal contacts                                                                                                                                                                                                    |  |  |  |  |

TABLE 1: Process parameters for deposited layers of fabricated devices.

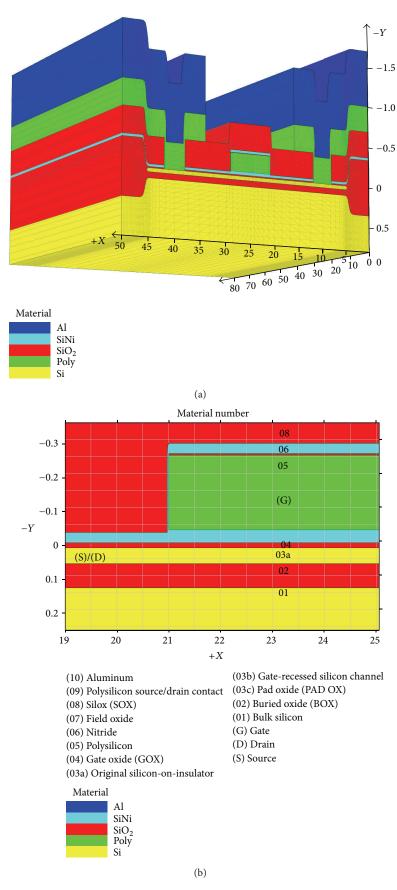

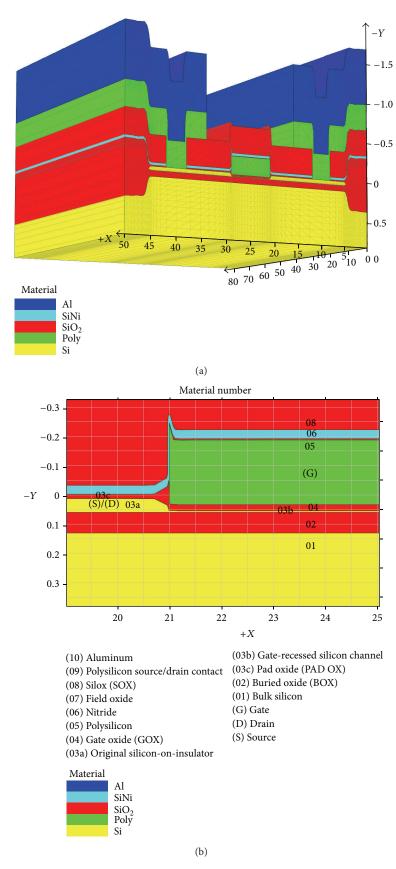

the devices as previously published [8]. In Figures 1(a) and 1(b) we present the simulated 3D structure of the ultrathin body (UTB) device, having a 46 nm thick body and channel and W/L ratio of 10 (80  $\mu$ m/8  $\mu$ m) and used as a reference device. In Figures 2(a) and 2(b), we show the simulated 3D structure of a ten-time reduced 4.6 nm thick channel obtained by the gate-recessed process, that is, the nanoscale body (NSB) device, sharing the same W and L values. As presented in Figures 1(a) and 2(a), the active region (source, gate, and drain terminals) is terminated by aluminum contacts (layer 10) in the vertical axis and limited by field oxide (layer 07) borders in the horizontal axis. The buried oxide (layer 02) is serving as a barrier between the bulk silicon (layer 01) and the gate-recessed silicon channel (layer 03).

Figure 2(b) represents a zoom-in of the gate-recessed channel, when the silicon layer was thinned from 46 nm to 4.6 nm. This points out advantage of the recessed process in which only the silicon channel is thinned while the source and drain regions and their respective extensions are remaining in their original (body) thickness. So the series resistance of the drain and of the source should not be affected *a priori* by the thinning process [14].

In addition to Figures 1 and 2, presenting a simulated TCAD cross-view of the device layers, a complementary list of the process parameters, most of which are used in the simulator, was presented in summarizing Table 1. Both the NSB and UTB devices were modeled in TCAD by applying almost the same process parameters used in their physical

fabrications. However, the NSB process deviated from its actual microfabrication in the timing of annealing steps. Due to quite difficult control of the channel doping and thus of the threshold voltage in NSB devices, only a single annealing step was applied after ion implantation for a very short period (1-2 min, 1000°C) to fit the measured threshold voltage. It was observed that a slight change in the annealing time in the simulation could be enough to convert the channel region into excessively doped silicon due to the donors' diffusion from the drain and source sides. Furthermore, since dry oxidation of polysilicon is not available in the used simulation tool, a deposition (plus annealing for 46 nm) step was inserted.

#### 3. Electrical Transfer Characteristics

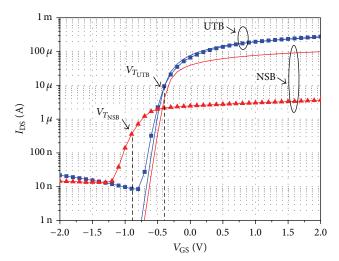

3.1. Measurements versus Simulations. I-V measurements (room temperature and dark conditions) were performed on both the UTB and the NSB's devices having a common channel width and length ( $W/L=80~\mu\text{m}/8~\mu\text{m}=10$ ) but a channel thickness ( $t_{\rm SI}$ ) of 46 nm and 4.6 nm, respectively. The corresponding transfer characteristics, that is, drain currents ( $I_{\rm DS}$ ) versus gate voltage ( $V_{\rm GS}$ ) from -2 to +2 V, were measured in the linear domain (constant low  $V_{\rm DS}=0.1~\text{V}$ ) and are presented in Figure 3. In addition we added the corresponding simulated characteristics (Apsys from Crosslight) using the default Canali or the so-called "beta"

FIGURE 1: (a) 3D cross view and (b) 2D zoom-in of UTB (46 nm thick SOI channel) device, using TCAD process simulation. X, Y, and Z axes are in micron units

FIGURE 2: (a) 3D cross view and (b) 2D zoom-in of NSB device (4.6 nm thick SOI channel), using TCAD process simulation. X, Y, and Z axes are in micron units

Default beta model analysis:

- ightharpoonup Measured  $I_{DS}$  for NSB 4.6 nm

- Simulated  $I_{DS}$  for NSB 4.6 nm

- → Measured I<sub>DS</sub> for UTB 46 nm

- Simulated  $I_{DS}$  for UTB 46 nm

FIGURE 3:  $I_{\rm DS}$ - $V_{\rm GS}$  transfer characteristics (semilog) measured at  $V_{\rm DS}=0.1$  V for UTB and NSB device having a channel thickness ( $t_{\rm SI}$ ) of 46 nm and 4.6 nm, respectively, and same W/L ratio. The default beta mobility model used in the TCAD device simulator is added as an initial guess model.

model [15] for the electron mobility as described in the next paragraph.

By increasing  $V_{\rm GS}$  from  $-2~\rm V$  to about  $-1~\rm V$ ,  $I_{\rm DS}$  slowly decreases, indicating a leakage phenomenon similar to the Gate Induced Drain Leakage (GIDL) observed for both classic and SOI-MOSFET devices [16]. The phenomenon is ignored in the simulation.

For  $V_{\rm GS}$  varying from  $-1\,{\rm V}$  to  $-0.5\,{\rm V}$ , the observed increasing steep is related to the subthreshold regime. We note that the subthreshold slope is strongly degraded by decreasing the channel thickness and may be due to a poor interface quality and/or a parasitic gate capacitance induced by the gate-recessed process. In the  $I_{\rm DS}$ - $V_{\rm GS}$  transfer curve, the threshold voltage  $(V_T)$  can be defined as the gate voltage for which the exponential extrapolation of subthreshold current deviates by 10% from the measured current [17]. This can be visualized by the highest point of the linear behavior in the semilog graph representation as shown in Figure 3. We preferred extracting  $V_T$  from the weak inversion region, since we argued that the strong inversion region, from which the  $V_T$  value is generally extracted, is already overwhelmed by the series resistance, for NSB device.

We note that the measured  $V_T$  value for NSB (-0.8 V) is lower than UTB's one (-0.4 V). However, for UTB's devices thinner than 10 nm typically,  $V_T$  is expected to increase by thinning the channel due to quantum effects as reported [18]. So, in our case, the  $V_T$  lowering could be rather related to a degradation of quality gate oxide that may occur during the thinning process.

3.2. Extraction of Field Dependent Mobility: Default Model versus Measurement. The TCAD device simulator (Apsys from Crosslight) uses a default field dependent mobility model, the so-called "beta" model [15], as described below for electron carrier:

$$\mu_n = \frac{\mu_{0n}}{\left(1 + (\mu_{0n} F/\nu_{\rm sn})^{\beta_n}\right)^{1/\beta_n}},\tag{1}$$

where  $\mu_{0n}$  is the low field electron mobility, F is the electrical field,  $\nu_{\rm sn}$  is the electron velocity saturation, and  $\beta_n$  is an exponent parameter (fixed to one as a default value).

The beta model in (1) was used as an initial guess model with its defaults values. However, in order to have a better agreement with experimental result, an additional mobility reduction factor of 0.728 was used for the UTB device. This factor is reasonable since the electron mobility in SOI film is expected to be lower than in the bulk. Afterwards, the same electrical simulation without the reduction factor was simulated on the 4.6 nm thick NSB device. The simulation results are presented in Figure 3.

Since  $V_{\rm DS}$  is fixed to 0.1 V, we can extract an *a priori* effective channel electron mobility using the following linear expression of the measured drain current:

$$\mu_n = \frac{I_{\rm DS}}{(W/L) C_{\rm ox} (V_{\rm GS} - V_T) V_{\rm DS}}.$$

(2)

This expression allows also extracting the mobility dependence of the electron mobility from the  $I_{\rm DS}\text{-}V_{\rm GS}$  TCAD simulations.

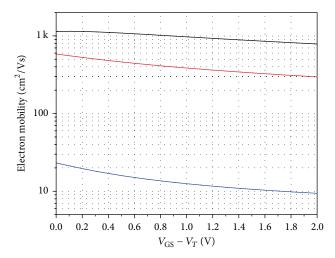

Figure 4 shows the dependence of the electron mobility relative to  $V_{\rm GS}-V_T$ , as extracted from (2) for the NSB device and compared to UTB used for reference. We can notice a large and unexpected discrepancy between the mobility values extracted from simulation and measurement for NSB. In order to get a match for the NSB device, an outstanding reduction factor of 0.042 should be used in contrast to the 0.728 factor used for UTB. Consequently, unlike UTB, the default beta model has failed to reproduce our experimental results for NSB. Note that the split C-V technique, usually employed for mobility extraction, was examined in a previous study [8]. But, we found out that a large series resistance can deteriorate the C-V characteristics consistently with our experimental results so the channel mobility cannot be discriminated by this technique for such NSB devices.

# 4. Methodology for TCAD Simulations of the NSB Transfer Characteristics

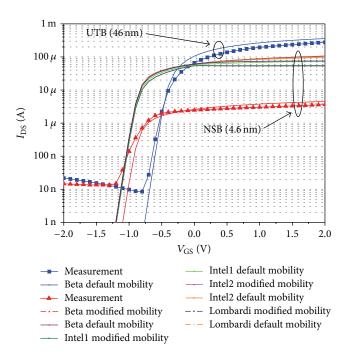

4.1. Limits of TCAD Standard Simulation Models. As a first approach, the transfer characteristics of the devices were simulated by existing mobility models which are available in the TCAD toolbox.

In Figure 5, a fitting of the mobility between the simulated NSB device and experimental result was presented. Using the same default beta model given in (1) and by introducing a prefactor of 0.042, obtained from the ratio between the simulated mobility and measured mobility values of the NSB

| Electron mobility model | Beta (=1) Intel 1 |                          | Intel 2 |                          |      | Lombardi (cgs units) |                 |       |                    |

|-------------------------|-------------------|--------------------------|---------|--------------------------|------|----------------------|-----------------|-------|--------------------|

| Parameter(s)            | Prefactor         | E <sub>crit</sub> (MV/m) | β       | E <sub>univ</sub> (MV/m) | α    | $B(10^7)$            | $\alpha (10^5)$ | β     | $\delta (10^{14})$ |

| Default value(s)        | 1                 | 4.2                      | 0.5     | 57.1                     | 1.02 | 4.75                 | 1.74            | 0.125 | 5.82               |

| Changed value(s)        | 0.042             | 4.5                      | 1       | 4.0                      | 1    | 4.75                 | 1.74            | 0.125 | 0.01               |

Table 2: Parameter(s) value(s) of the respective standard electron mobility models. Changed value(s) correspond to a nonphysical behavior of the simulated transfer characteristics (i.e., null transconductance).

Default beta model analysis:

— Extracted from simulation for UTB 46 nm

Extracted from simulation for NSB 4.6 nm

Extracted from measurement for NSB 4.6 nm

Figure 4: The effective electron mobility versus  $V_{\rm GS}-V_T$  relationship (semilog) extracted from the simulated transfer characteristics using the default beta model for UTB and NSB devices. For comparison the electron mobility extracted from the measurement for NSB device.  $V_{\rm DS}$  is fixed to 0.1 V.

device (see Figure 4), it is possible to get good agreement with the experimental result of the 4.6 nm device for gate voltages below -0.5 V (beta modified mobility curve). Above -0.5 V, the  $I_{\rm DS}$ - $V_{\rm GS}$  characteristics start to deviate from the experimental data indicating a discrepancy of the beta model. It is important to note that a prefactor was preferably used instead of manipulating the model parameters  $V_{\rm sat}$  and  $\beta$  in (1)

Other existing models of mobility reduction, due to transverse field (perpendicular to the MOSFET channel), have been implemented as follows and plotted in Figure 5.

(1) The model "Intell" based on pisces-2ET manual (Stanford University) [19] defines a factor to reduce the mobility under the channel:

$$r_{\text{perp}} = \frac{\mu}{\mu_0} = \left(1 + \frac{E_{\text{perp}}}{E_{\text{crit}}}\right)^{-\beta},\tag{3}$$

where  $E_{\rm perp}$  is the field perpendicular to the SiO<sub>2</sub>/Si interface and  $\mu_0$  is bulk mobility value for electron in silicon at 300 K (1500 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>).  $E_{\rm crit}$  and  $\beta$  are the critical field and the exponent factor, respectively, indicated in Table 2.

FIGURE 5:  $I_{\rm DS}$ - $V_{\rm GS}$  (semilog) for experimental and simulation data. The presented NSB's  $I_{\rm DS}$ - $V_{\rm GS}$  are based on all the available field dependent mobility models in TCAD device simulator. Default and changed parameters are presented in Table 2.  $V_{\rm DS}$  is fixed to 0.1 V.

(2) The model "Intel2" also based on pisces-2ET manual (Stanford University) defines another kind of factor to reduce the mobility under the channel according to the so-called "universal mobility curve" as follows:

$$r_{\text{perp}} = \frac{\mu}{\mu_0} = \left[1 + \left(\frac{E_{\text{perp}}}{E_{\text{univ}}}\right)^{\alpha}\right]^{-1}.$$

(4)

(3) A more refined model called Lombardi's model [20] proposes to integrate the contributions to mobility from different mechanisms as follows:

$$\frac{1}{\mu} = \frac{1}{\mu_{\rm ac}} + \frac{1}{\mu_{\rm srf}} + \frac{1}{\mu_0},\tag{5}$$

where  $\mu_0$  is this time of the mobility due to longitudinal field/hot-carrier effect. The other terms are due

to acoustic phonons and surface roughness defined, respectively, by

$$\mu_{\rm ac} = \frac{B}{E_{\rm perp}} + \frac{\alpha N^{\beta}}{\left(T_L E_{\rm perp}^{1/3}\right)},\tag{6}$$

$$\mu_{\rm srf} = \frac{\delta}{E_{\rm perp}^2},\tag{7}$$

where  $T_L$ , B, and N are, respectively, the lattice temperature, velocity equivalent factor, and the average doping concentration ( $10^{17}$  cm<sup>-3</sup>). At room temperature, for very thin channel, the surface roughness is the dominant back-scattering mechanism (see [1, chapter 7]). So we only modified the  $\delta$  parameter of the  $\mu_{\rm srf}$  component in Lombardi's model.

The mentioned models were modified to fit the NSB experimental characteristics till getting a nonphysical behavior (i.e., null transconductance, except the beta model). The corresponding parameters are shown in Table 2.

The transfer characteristics simulated using all the above models (default and modified) are added in Figure 5 for NSB device. However, except the beta model, the modified models are still presenting a discrepancy of more than one order of magnitude compared to the measurement. But even in the modified beta model the prefactor should be changed by a small factor leading to very low electron mobility for such kind of devices (less than  $10~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$ ). These results lead us to insert the series resistance influence in the transport model of the NSB device.

4.2. Application of  $R_{\rm SD}$  versus  $V_{\rm GS}$  Model to NSB Device. In order to describe the NSB measured transfer characteristic by the influence of a series resistance, we used the gate voltage and body thickness dependent series resistance model, presented in [8] which is considered as the access resistance (=  $V_{\rm DS}/I_{\rm DS}$ ). Consider

$$R_{\rm SD} = \frac{R_{\rm SD0}^* e^{-t_{\rm si}/t_0}}{1 + \theta^* V_{\rm GS}/t_{\rm si}},\tag{8}$$

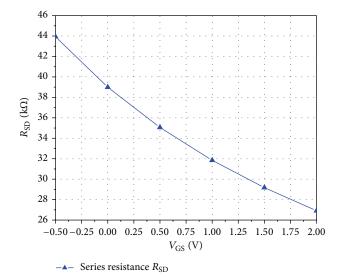

with  $R_{\rm SD0}^* = 4.54 \, {\rm M}\Omega$ ,  $t_0 = 1.03 \, {\rm nm}$ , and  $\theta^* = 1.1 \, {\rm nm} \cdot {\rm V}^{-1}$ . A resistance extraction was made for  $t_{\rm SI} = 4.6 \, {\rm nm}$  and gate voltages between -0.5 and 2V and shown in Figure 6.

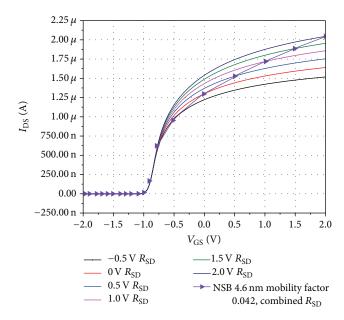

4.3. Influence of  $R_{\rm SD}$  on the Simulated Transfer Characteristics. The  $I_{\rm DS}$ - $V_{\rm GS}$  was simulated using the field dependent beta model without the reduction mobility factor of 0.042. The series resistance can be included in the TCAD device simulator as an external lumped element but for a fixed value of  $V_{\rm GS}$ . Thus we simulated  $I_{\rm DS}$ - $V_{\rm GS}$  characteristics for each extracted resistance values in the range of  $-0.5~{\rm V}$  to  $2~{\rm V}$  with 0.5 V steps (six different values according to Figure 6). The influence of the  $R_{\rm SD}$  voltage dependence on  $I_{\rm DS}$ - $V_{\rm GS}$  can be simulated by a postprocessing of the above simulated characteristics which is shown in Figure 7. Indeed, for a given  $I_{\rm DS}$ - $V_{\rm GS}$  curve corresponding to a  $R_{\rm SD}$  given for a particular

FIGURE 6:  $R_{\rm SD}$  versus  $V_{\rm GS}$  relation for NSB with 4.6 nm channel thick given by (8).

Figure 7: The variation of simulated  $I_{\rm DS}$ - $V_{\rm GS}$  for each extracted resistance values in the range of  $-0.5~\rm V$  to  $2~\rm V$  with  $0.5~\rm V$  steps.  $V_{\rm DS}$  is fixed to  $0.1~\rm V$ .

$V_{\rm GS}$ , for example, -0.5 V, the current value is sampled at this particular voltage  $V_{\rm GS}$ . The process is then repeated for each  $I_{\rm DS}$ - $V_{\rm GS}$  curve at the  $V_{\rm GS}$  value corresponding to the next  $R_{\rm SD}$  step value. The reconstructed  $I_{\rm DS}$ - $V_{\rm GS}$  characteristic from the sampled  $I_{\rm DS}$  values is shown as the graph with triangle symbols in Figure 7.

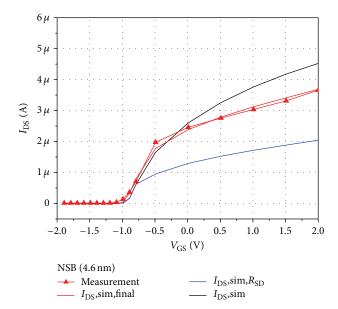

In Figure 8, we compare our reconstructed characteristic from Figure 7 (now called  $I_{\rm DS,sim,RSD}$ ) to the measured one and to the simulated one from the beta model with the reduction mobility factor of 0.042 only ( $I_{\rm DS,sim}$ ). While the latter is higher than the measured characteristic, it appears that reconstructed one is now lower. Mobility reduction and

Figure 8: Simulated  $I_{\rm DS}$ - $V_{\rm GS}$  data including the resistance in series to the drain terminal compared to the measured one for NBS device. An exponent value of 0.93 in (9) gave the best fit to measurement.  $V_{\rm DS}$  is fixed to 0.1 V.

series resistance effect are in competition to reduce the drain current but each of them is dominating in a particular range of  $V_{\rm GS}$  values (below -0.5 V and above -0.5 V, resp.). Consequently we suggest unifying both simulated characteristics to simulate the final current  $I_{\rm DS,sim,final}$  according the following equation inspired from Matthiessen's mobility-like law:

$$I_{\text{DS,sim,final}} = \left(\frac{I_{\text{DS,sim}}I_{\text{DS,sim,RSD}}}{I_{\text{DS,sim}} + I_{\text{DS,sim,RSD}}}\right)^{n}.$$

(9)

It was found that an exponent value of n = 0.93 gave the best fit to the experimental characteristics, as it is presented in Figure 8.

#### 5. Conclusion

Nanoscale SOI-MOSFET devices were fabricated using a selective recessed gate thinning process to get channel thicknesses scaling from 46 nm down to 4.6 nm. We show that the anomalous degradation of electrical characteristics of the latter can be modeled by a gate controlled series resistance rather than merely by a mobility model. Using TCAD tools, the devices' transfer characteristics were simulated using the series resistance model combined with a factorized mobility model. Based on simulation results, it could be better understood that for low gate voltage the degraded electron mobility may be the dominant factor while at high gate voltage the series resistance becomes the dominant factor. Among various tested mobility models we have found out that the best fit is obtained when combining the modified beta mobility model with the gate voltage dependent series model. We suggest that this semiempirical modeling approach may be useful as a TCAD embedded tool to model the behavior of other nanodevices for which series resistance and/or mobility degradation is of a great concern.

#### **Conflict of Interests**

The authors have no conflict of interests associated with this paper.

#### References

- [1] D. Esseni, P. Palestri, and L. Selmi, *Nanoscale MOS Transistors*, *Semi-Classical Transport and Applications*, Cambridge University Press, Cambridge, UK, 2011.

- [2] A. Karsenty, A. Sa'ar, N. Ben-Yosef, and J. Shappir, "Enhanced electroluminescence in silicon-on-insulator metal-oxide-semiconductor transistors with thin silicon layer," *Applied Physics Letters*, vol. 82, no. 26, pp. 4830–4832, 2003.

- [3] M. Nawaz, S. Decker, L.-F. Giles, W. Molzer, and T. Schulz, "Evaluation of process parameter space of bulk FinFETs using 3D TCAD," *Microelectronic Engineering*, vol. 85, no. 7, pp. 1529– 1539, 2008.

- [4] A. Biswas, S. S. Dan, C. L. Royer, W. Grabinski, and A. M. Ionescu, "TCAD simulation of SOI TFETs and calibration of non-local band-to-band tunneling model," *Microelectronic Engineering*, vol. 98, pp. 334–337, 2012.

- [5] D. Esseni, P. Palestri, and L. Selmi, Nanoscale MOS Transistors, Semi-Classical Transport and Applications, Cambridge University Press, Cambridge, UK, 2011.

- [6] W. Ke, S. Zhang, X. Liu, and R. Han, "Source/drain resistance of UTB SOI MOSFET," in *Proceedings of the IEEE Conference on Electron Devices and Solid-State Circuits*, pp. 405–408, 2005.

- [7] J. C. Yoon, A. Hiroki, and K. Kobayashi, "Structure dependence of reduced saturation current influenced by source and drain resistances for 17 nm MOSFETs," in *Proceedings of the 10th International Meeting for Future of Electron Devices, Kansai (IMFEDK '12)*, pp. 1–2, May 2012.

- [8] A. Karsenty and A. Chelly, "Modeling of the channel thickness influence on electrical characteristics and series resistance in gate-recessed nanoscale SOI MOSFETs," Active and Passive Electronic Components, vol. 2013, Article ID 801634, 10 pages, 2013

- [9] G. Ghibaudo, "New method for the extraction of MOSFET parameters," *Electronics Letters*, vol. 24, no. 9, pp. 543–545, 1988.

- [10] C. Mourrain, B. Cretu, G. Ghibaudo, and P. Cottin, "New method for parameter extraction in deep submicrometer MOS-FETs," in *Proceedings of the International Conference on Micro*electronic Test Structures (ICMTS '00), 2000.

- [11] A. Cros, S. Harrison, R. Cerutti, P. Coronel, G. Ghibaudo, and H. Brut, "New extraction method for gate bias dependent series resistance in nanometric double gate transistors," in *Proceedings of the IEEE International Conference on Microelectronic Test Structures (ICMTS '05)*, vol. 18, pp. 69–74, IEEE, April 2005.

- [12] D. Fleury, A. Cros, H. Brut, and G. Ghibaudot, "New Y-function-based methodology for accurate extraction of electrical parameters on nano-scaled MOSFETs," in *Proceedings of the IEEE Conference on Microelectronic Test Structures (ICMTS '08)*, pp. 160–165, IEEE, Edinburgh, UK, March 2008.

- [13] A. Karsenty and A. Chelly, "Application, modeling and limitations of Y-Function based methods for massive series resistance in nanoscale SOI MOSFETs," *Solid-State Electronics*, vol. 92, pp. 12–19, 2014.

- [14] K. Uchida and S.-I. Takagi, "Carrier scattering induced by thickness fluctuation of silicon-on-insulator film in ultrathin-body metal-oxide-semiconductor field-effect transistors," *Applied Physics Letters*, vol. 82, no. 17, pp. 2916–2918, 2003.

- [15] V. O. Turin, "A modified transferred-electron high-field mobility model for GaN devices simulation," *Solid-State Electronics*, vol. 49, no. 10, pp. 1678–1682, 2005.

- [16] J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, "Gate-induced drain leakage in FD-SOI devices: what the TFET teaches us about the MOSFET," *Microelectronic Engineering*, vol. 88, no. 7, pp. 1301–1304, 2011.

- [17] B. El-Kareh, W. R. Tonti, and S. L. Titcomb, "Submicron MOSFET parameter extraction technique," *IBM Journal of Research and Development*, vol. 34, no. 2-3, pp. 243–249, 1990.

- [18] Y. Omura, S. Horiguchi, M. Tabe, and K. Kishi, "Quantum-mechanical effects on the threshold voltage of ultrathin-SOI nMOSFETs," *IEEE Electron Device Letters*, vol. 14, no. 12, pp. 569–571, 1993.

- [19] PISCES-2ET and Its Application Subsystems, Stanford University, 1994, http://www-tcad.stanford.edu/tcad/programs/pisces\_2et\_and\_apps.pdf.

- [20] C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, "A physically based mobility model for numerical simulation of non-planar devices," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 7, no. 11, pp. 1164–1171, 1988.

Submit your manuscripts at http://www.hindawi.com