Hindawi Publishing Corporation Active and Passive Electronic Components Volume 2016, Article ID 7201760, 11 pages http://dx.doi.org/10.1155/2016/7201760

### Research Article

# Design and Simulation of a 6-Bit Successive-Approximation ADC Using Modeled Organic Thin-Film Transistors

## Huyen Thanh Pham, 1,2 Thang Vu Nguyen, 1 Loan Pham-Nguyen, 1 Heisuke Sakai, 3 and Toan Thanh Dao 2

<sup>1</sup>School of Electronics and Telecommunications, Hanoi University of Science and Technology, No. 1, Dai Co Viet Street, Hai Ba Trung District, Hanoi 10000, Vietnam

Correspondence should be addressed to Huyen Thanh Pham; huyenktdt@utc.edu.vn, Thang Vu Nguyen; thang.nguyenvu@hust.edu.vn, and Toan Thanh Dao; daotoan@utc.edu.vn

Received 20 December 2015; Revised 8 February 2016; Accepted 15 February 2016

Academic Editor: Abdelkarim Mercha

Copyright © 2016 Huyen Thanh Pham et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

We have demonstrated a method for using proper models of pentacene P-channel and fullerene N-channel thin-film transistors (TFTs) in order to design and simulate organic integrated circuits. Initially, the transistors were fabricated, and we measured their main physical and electrical parameters. Then, these organic TFTs (OTFTs) were modeled with support of an organic process design kit (OPDK) added in Cadence. The key specifications of the modeled elements were extracted from measured data, whereas the fitting ones were elected to replicate experimental curves. The simulating process proves that frequency responses of the TFTs cover all biosignal frequency ranges; hence, it is reasonable to deploy the elements to design integrated circuits used in biomedical applications. Complying with complementary rules, the organic circuits work properly, including logic gates, flip-flops, comparators, and analog-to-digital converters (ADCs) as well. The proposed successive-approximation-register (SAR) ADC consumes a power of 883.7  $\mu$ W and achieves an ENOB of 5.05 bits, a SNR of 32.17 dB at a supply voltage of 10 V, and a sampling frequency of about 2 KHz.

#### 1. Introduction

Although Si-based integrated circuits (ICs) are dominant due to their excellent specifications, such as high precision, high speed, and ultra-low power consumption [1–3], organic ICs have recently emerged as a potential candidate for many applications, for instance, wearable devices and medical sensors. Its unique advantages over Si-based counterpart include flexibility, biocompatibility, and low-cost process [4–6]. In particular in research and development of organic IC, time and cost could be reduced significantly with computer-aided design (CAD) tools [7–10]. Among CAD tools, HSPICE and Cadence Virtuoso are famous for their high accuracy, multifunction, and ease to use. The VLSI group at University of Minnesota built an organic process design kit (OPDK)

added in Cadence [11]. The tool supports organic integrated circuit design and simulation, but its library has only a P3HT P-channel OTFT and a CNT unipolar field-effect transistor (FET). In other works, the Spice level 1 MOS model was used to simulate the pentacene circuits [12]. However, a big difference between simulation and measurement results obviously occurred, since the model embraces a few electrical parameters of the charge mobility, threshold voltage, early voltage, and capacitive behavior.

On the other hand, at the circuit level, an analog-digital converter (ADC) plays an important role in signal processing due to its connection between analog and digital world. So far, the organic ADCs have been mainly constructed with P-type technology and those exhibit many limitations, for

<sup>&</sup>lt;sup>2</sup>Faculty of Electrical-Electronic Engineering, University of Transport and Communications, No. 3, Cau Giay Street, Dong Da District, Hanoi 10000, Vietnam

<sup>&</sup>lt;sup>3</sup>Japan Advanced Institute of Science and Technology, 1-1 Asahidai, Nomi, Ishikawa 923-1292, Japan

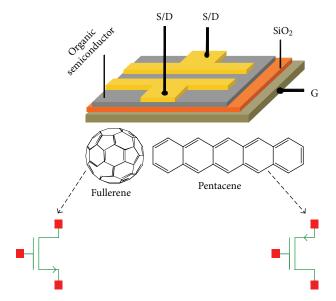

FIGURE 1: Illustrations of OTFT layout, fullerene, and pentacene molecular semiconductors and circuit symbols of fullerene N or pentacene P-channel OTFTs.

example, low gain, narrow bandwidth, low speed, and high power consumption [12–14].

In this work, widely used fullerene and pentacene OTFTs were fabricated and characterized. Subsequently, we utilized the Spice level 61 with 29 parameters, which originally is developed for amorphous silicon transistor, to improve OPDK models for such OTFTs. Electrical characteristics obtained by simulation matched very well with those from the experiments. The well-developed models of both P-type and N-type OTFTs allow construction of a complex circuit with complementary technology. In later progress, organic logic gates, flip-flops, comparators, and successive-approximation-register (SAR) ADCs were designed and verified in Cadence. The simulation results indicated that our 6-bit SAR ADC operated at a high sampling frequency up to 2 KHz and a relatively low power of about 883  $\mu$ W.

#### 2. Fabrication and Modeling OTFTs

Figure 1 shows the layout structure of OTFTs and molecular structures of pentacene and fullerene together with the OTFT symbols in Cadence. The OTFTs were fabricated on SOI (Silicon-On-Insulator) wafer with a heavily doped Si (n + Si, resistivity: 1–100  $\Omega$  cm) gate electrode coated with a 50 nm SiO $_2$  insulating layer. The experimental method was detailed in previous report [15]. In short, the substrate was cleaned by ultrasonication; 50 nm thick fullerene and 30 nm thick pentacene layers were thermally deposited on SOI via a designed shadow mask, for N-channel and P-channel, respectively, at a base pressure of  $2 \times 10^{-6}$  torr and deposition rate of 0.1 nm s $^{-1}$ . Finally, Au source-drain electrodes were formed by thermal evaporation at a deposition rate of 0.3 nm s $^{-1}$  through a designed shadow mask under a certain pressure of  $2 \times 10^{-6}$  torr. The channel length L and geometry factor

TABLE 1: Main parameters in the OTFT models.

| Parameters                       | O                    | ГҒТѕ                 |

|----------------------------------|----------------------|----------------------|

|                                  | P-channel            | N-channel            |

| $\mu_0 \text{ [cm}^2/\text{Vs]}$ | 0.25                 | 0.4                  |

| $V_{\rm th} [{ m V}]$            | -1.62                | 2                    |

| $C_{\rm diel} [\mu F/m^2]$       | $6.91 \times 10^{2}$ | $6.91 \times 10^{2}$ |

| $V_{aa}$                         | 14.695               | 20                   |

| γ                                | 5.28                 | 0.02                 |

| λ                                | 0.001                | 0.001                |

| m                                | 3.5                  | 4                    |

| $\alpha_{\mathrm{sat}}$          | 0.2                  | 0.73                 |

W/L of OTFT devices were 50  $\mu$ m and 40, respectively. Electrical measurements of the OTFTs were carried out with the Keithley 4200 semiconductor characterization system in a dry nitrogen atmosphere at room temperature in a dark probe station.

In OTFT elements, drain-source current  $I_{\rm DS}$  includes accumulation current and leakage current [15], which is described as

$$I_{DS} = \frac{W}{L} C_{\text{diel}} \mu_0 \left( \frac{V_{GS} - V_{\text{th}}}{V_{\text{aa}}} \right)^{\gamma} \left( V_{GS} - V_{\text{th}} \right) (1 + \lambda V_{DS})$$

$$\cdot \frac{V_{DS}}{\left[ 1 + \left( V_{DS} / \alpha_{\text{sat}} \left( V_{GS} - V_{\text{th}} \right) \right)^m \right]^{1/m}} + V_{DS} SIGMA0, \tag{1}$$

where  $C_{\rm diel}$  is the gate dielectric capacitance,  $\mu_0$  is the mobility,  $V_{\rm GS}$  is the gate-source voltage,  $V_{\rm th}$  is the threshold voltage,  $V_{\rm aa}$  is the characteristic voltage for field-effect mobility,  $\gamma$  is the power-law mobility,  $\lambda$  is the output conductance,  $\alpha_{\rm sat}$  is the saturation modulation, m is the knee shape parameter, and SIGMA0 is the minimum leakage current parameter. All of them would appear in model files of OTFT elements, so they need to be specified as accurately as possible.

Among those values, the W, L, and  $C_{\rm diel}$  are the physical structure parameters;  $\mu_0$ ,  $V_{\rm th}$ ,  $\gamma$ ,  $V_{\rm aa}$ , and  $\alpha_{\rm sat}$  are extracted from the experimental data [10, 15, 16]. The others are fitting parameters determined by simulating with numerical different values. Accordingly, the optimized parameters of the OTFT models are summarized in Table 1. By using these parameters in Cadence, it allows replicating the electrical behaviors of OTFT elements.

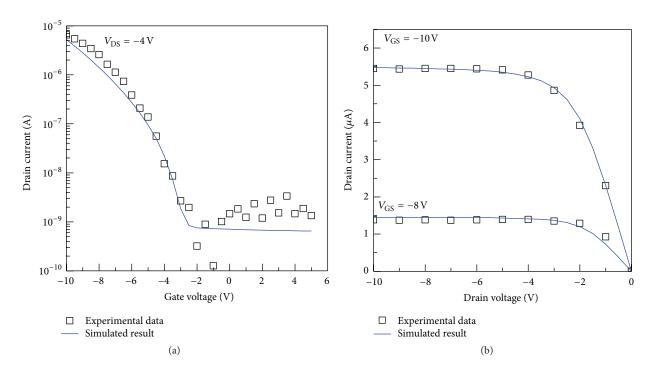

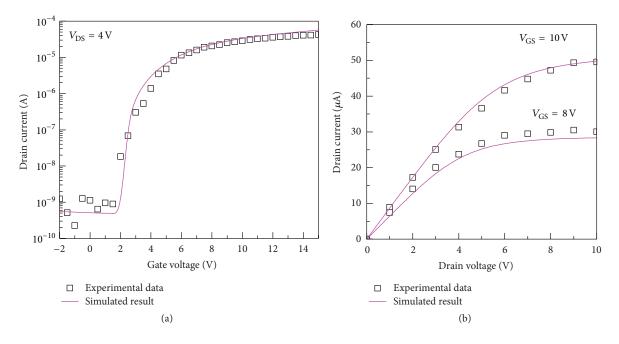

Figures 2 and 3 indicate the transfer and output characteristics from simulation results of P-channel and N-channel OTFTs, which fit well to the experimental curves. These agreements corroborate that our proposed devices are modeled correctly; hence, it is acceptable to use them in organic integrated circuit designs.

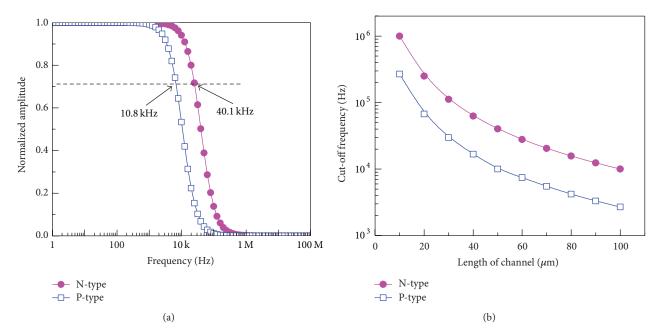

Furthermore, we have also investigated operating frequencies of the elements so as to ensure that proposed circuits using these ones would be employed in appropriate applications. The frequency response characteristics at  $L=50\,\mu\mathrm{m}$  are reflected in Figure 4(a). It is a general concept that the cut-off frequency  $f_c$  is defined as the frequency at which

FIGURE 2: Characteristics of pentacene P-channel obtained from experiment and simulation: (a) transfer and (b) output.

FIGURE 3: Characteristics of fullerene N-channel obtained from experiment and simulation: (a) transfer and (b) output.

the ratio of the output/input has a magnitude of 0.707. As can be realized in Figure 4(a), the  $f_c$  is 40.1 KHz and 10.8 KHz for the N-type and P-type, respectively.

The  $f_c$  in N-channel OTFT towers over that in P-channel one due to its higher mobility, as listed in Table 1. The  $f_c$  versus L is summarized in Figure 4(b). When the L varies from 100  $\mu$ m to 10  $\mu$ m the cut-off frequency  $f_c$  increases from several KHz to several MHz. In terms of frequency,

the operating frequencies cover all biosignal frequency ranges in which the highest value is 10 KHz [17].

#### 3. Organic Complementary Logic Gates

VLSI technology fundamentally is comprised of digital logic gates. To further confirm that our designed electronic circuits

FIGURE 4: (a) Frequency response characteristics at  $L = 50 \, \mu \text{m}$ . (b) Cut-off frequency versus length of channel.

are biocompatible, in this section, some basic organic complementary digital circuits, including a transmission gate, an inverter, a NOR, and a NAND, are created and verified with a 10 V power supply voltage and about 10 KHz input signals. The applied voltage supply of 10 V to set the OTFT elements works in deep accumulation mode. The chosen working frequency is to adapt to the highest biopotential signal frequency as above-mentioned.

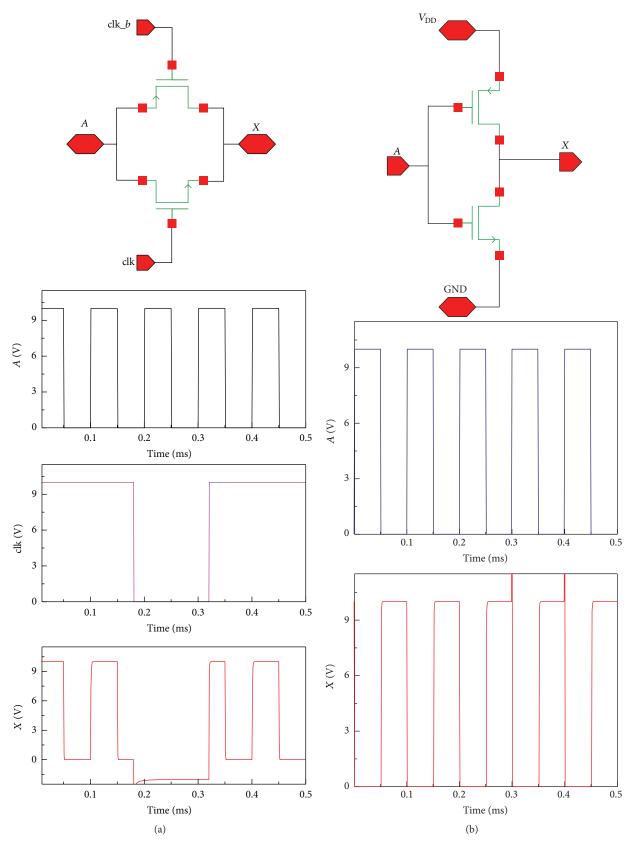

3.1. Transmission Gate and Inverter. We assume that the voltage levels of 10 and 0 V correspond to a logical "1" and "0," respectively. Figure 5(a) shows the schematic and waveforms of the transmission gate, which is indeed a clocked circuit composing a P-channel and an N-channel transistor in parallel. The input signal passes through the gate when the clock is high only (in Figure 5(a)).

Figure 5(b) displays the schematic of the inverter and its waveforms. As defined, the output voltage  $(V_X)$  is invertible to the input voltage  $(V_A)$  in high or low levels. The simulation results suggest that the designed CMOS circuits operate properly.

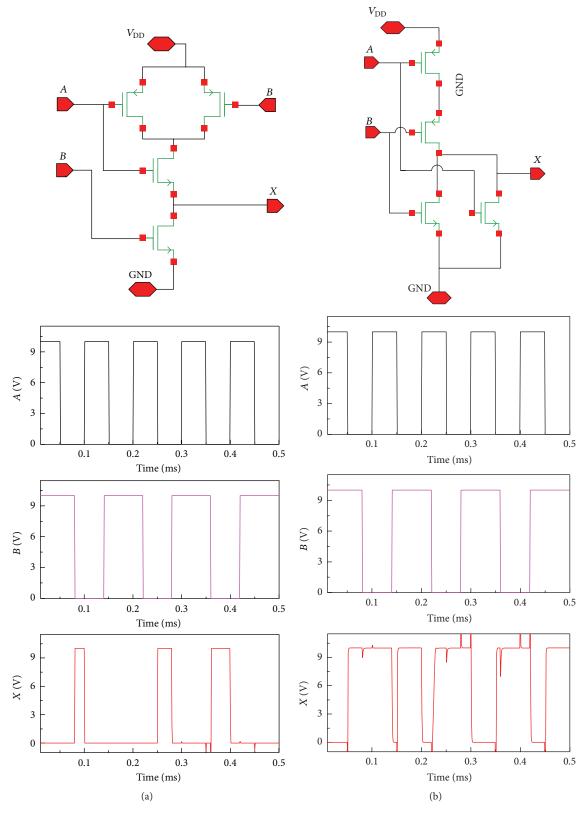

3.2. NOR and NAND. Figure 6 presents the schematics and waveforms of the organic two-input CMOS NOR and NAND circuits. With the NOR gate in Figure 6(a), P-channel OTFTs firstly connect in parallel to form the pull-up network, and then, following the complementary design rule, the pull-down network is constructed of N-channel OTFT elements in serial connection. Similarly, in order to build the NAND gate in Figure 6(b), P-channel OTFTs are in serial, while N-channel OTFT elements are in parallel connection. The frequencies of A and B inputs are set to be 10 and 7.14 KHz, respectively. As can be realized in Figure 6, the outputs comply with the truth tables of NOR and NAND gates.

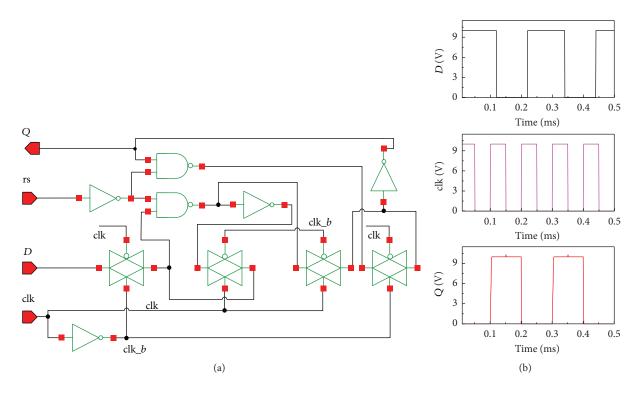

3.3. D Flip-Flop (D-FF). Flip-flop is a basic storage element in digital electronics with two stable states "1" and "0." Indeed, D-FF is most essential element in registers and digital logic blocks discussed in the next sections. Figure 7(a) presents a circuit diagram of D flip-flop composed by the logic gates designed in the aforementioned section. The observed waveforms in Figure 7(b) demonstrate that output Q equals input D at the rising edges of clk pulse; otherwise, Q does not change. It means Q is a "delay" of D, as expected.

#### 4. 6-Bit Organic Fully Differential SAR ADC

Demand for portable compact products in modern life is increasing, so most integrated circuit designers desire to achieve energy saving goals. As for ADCs, the SAR structure is worth doing at all since its total power consumption is much lower than that in other ADC configurations, such as flash, delta-sigma, or pipelined ADCs [20].

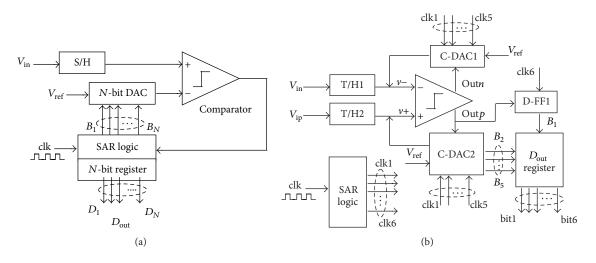

4.1. Circuit Design. Figure 8(a) displays a conventional structure of SAR ADC, which is constructed of a minimum number of analog blocks, including a Sample/Hold (S/H), a Digital-to-Analog Converter (DAC), a comparator in connection with a SAR logic, and a register. In this work, to reduce as much as possible power consumption, we have employed simple schematics for the ADC with a limited number of transistor elements complying with complementary rules. The fully differential 6-bit SAR ADC having two analog inputs and six digital outputs was designed and simulated with the OPDK in Cadence Virtuoso environment, as simplified in Figure 8(b). The ADC consisted of two track and hold (T/H) blocks, two capacitive DACs, a comparator, a SAR logic, and an output register.

FIGURE 5: Schematics (top) and waveforms (bottom) of (a) transmission gate and (b) inverter.

Figure 6: Schematics (top) and waveforms (bottom) of (a) NOR and (b) NAND.

FIGURE 7: D flip-flop: (a) topology and (b) simulation result at a clock frequency of 10 KHz.

FIGURE 8: (a) Conventional structure of a SAR ADC. (b) Simplified structure of 6-bit SAR ADC.

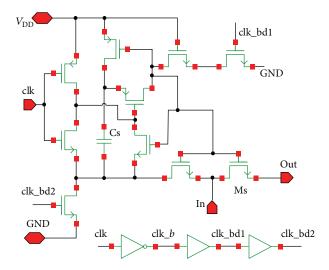

Figure 9 describes the T/H circuit as a bootstrapped switch with the input large transistor Ms [21]. The size of Ms affects the linearity since drain-source capacitance of Ms couples to the Cs to sample the input signal. Both T/H blocks sample and hold input signals during conversion time. Their outputs connect to the inputs of the dynamic comparator.

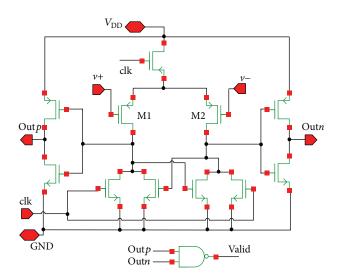

It should be noted that the basic comparator structure is a two-stage comparator, including an amplifier and

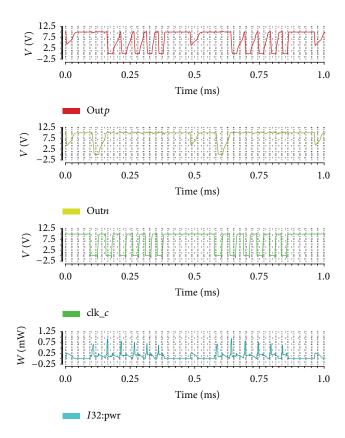

a positive feedback latch. Although that circuit is less sensitive to the effects of kickback noise and device offset, it consumes much more power. In contrast, our design aims to reduce power consumption; hence, the dynamic comparator is implemented with clock signals in order not to draw static currents. Figure 10 presents the schematic of the dynamic latch comparator with a P-type input differential pair M1-M2. When the clk signal goes to high, the outputs outp and outn

FIGURE 9: Schematic of track and hold block.

FIGURE 10: Schematic of dynamic latch comparator.

are high, too. When the clk goes to low, the differential pair compares v+ and v- resulting in output outp or outn being either high or low.

As for DACs, some architectures are well-known, including current-steering, C-2C, and capacitive switch types. The conventional N-bit capacitive DAC (C-DAC) uses a binary-weighted capacitor array leading to the total capacitance of  $2^N$  unit capacitor. This structure obtains better linearity, but the large number of capacitors expands the circuit dimension rapidly and consumes lots of energy. However, the value of total capacitance of one C-DAC circuit in Figure 8(b) can be reduced a half since the most significant bit (MSB) is estimated separately [22]. The control algorithm of this ADC requires that the comparator sets the MSB to 1 if  $V_{\rm ip}$  is higher than  $V_{\rm in}$ ; otherwise the MSB is 0. Sequentially, the N-bit ADC pushes MSB to LSB after N cycles of clock signals.

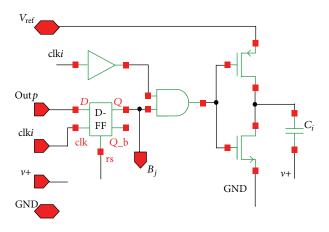

FIGURE 11: Typical subblock in C-DAC2.

That is, after several comparison cycles, one conversion step is complete; therefore, the SAR ADC exhibits limited speed. The DAC embraces 5 subblocks; a typical subblock circuit is presented in Figure 11 in which i is from 1 to 5 and j is from 6 to 2. The capacitance of unit capacitor is  $C_0$ , then  $C_5$  equals  $C_0$ , and  $C_{i-1}=2C_i$ . This induces that the total capacitance of one C-DAC circuit is  $31C_0$ . The C-DAC1 is designed similarly with inputs Outn and v-.

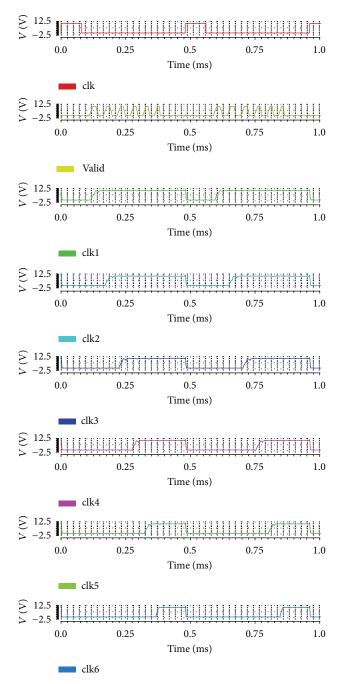

The SAR logic comprises 6 D-FFs in serial to generate clk1 to clk6. Figure 8(b) shows that the clock signals from clk1 to clk5 are connected to C-DACs for controlling 5 capacitor arrays, while clk6 is connected to D-FF1 to push the MSB. The output register is also constructed with D-FFs to store all bits  $B_i$  from the C-DAC2 and the MSB ( $B_1$ ).

4.2. Simulation Results. A power supply voltage of 10 V, a reference voltage of 5 V, a  $\sim$ 2 KHz clock frequency, and a 2 V, 10 Hz sine wave input signal were provided to simulate the designed SAR ADC.

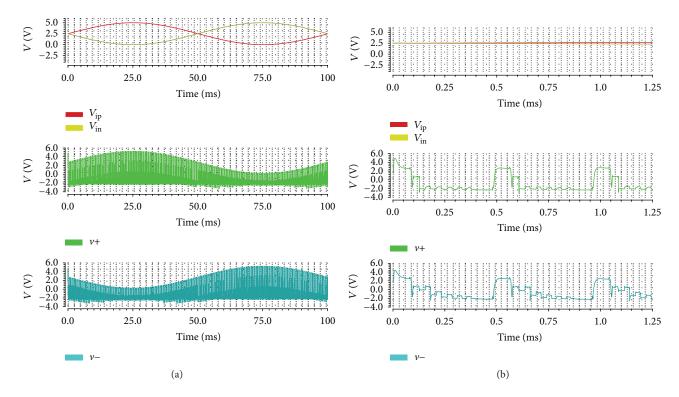

Figure 12 presents a cycle of inputs and outputs of the T/H and its magnitude on time-axis. The data indicates that the circuit samples and holds the input signals during the conversion duty.

Simulation results in Figure 13 also attest the main power consumption at rising and falling edges of clock pulses of the dynamic comparator. Consequently, its average dissipated energy reduces significantly to about 112  $\mu$ W. The simulation process also points out that the higher input voltage makes the power decrease. This is because of a reduction in the drain current resulting from the lower gate-source voltages of M1 and M2 (in Figure 10).

The timing diagram of the SAR logic is given in Figure 14. Each clki goes to high sequentially at the rising edges of the valid signal, which is created based on the comparator outputs, as seen in Figure 10. All of the clock pulses go to low at the rising edge of the primary clk signal to end one conversion step.

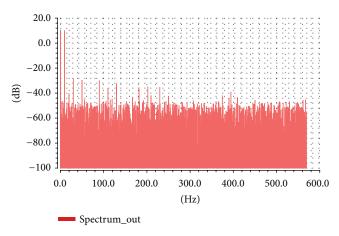

Dynamic performance of an ADC needs to use Fast Fourier Transform (FFT) test method to measure effective

TABLE 2: Performance summary of current organic ADCs.

| Specification                  | [12] <sup>a</sup>       | $[14]^{b}$              | [18] <sup>b</sup>      | [19] <sup>b</sup> | This work <sup>c</sup>  |

|--------------------------------|-------------------------|-------------------------|------------------------|-------------------|-------------------------|

| Organic semiconductor material | Pentacene (only P-type) | Pentacene (only P-type) | DNTT<br>F16CuPc<br>SAM | PEN foil<br>SAM   | Pentacene and fullerene |

| Structure                      | Delta-sigma             | VCO-based               | SAR C-2C               | SAR R-2R          | C-SAR                   |

| Supply power [V]               | 15                      | 20                      | 3                      | 40                | 10                      |

| Resolution [bit]               | 5                       | 10                      | 6                      | 4                 | 6                       |

| ENOB [bit]                     | $4.69^{\dagger}$        | 6                       | N/A                    | 2.96              | 5.05                    |

| SNR [dB]                       | $30^{\dagger}$          | 48                      | N/A                    | 19.6              | 32.17                   |

| Sampling frequency [Hz]        | 500                     | <40                     | 100                    | 4.17              | 2000                    |

| Power consumption [ $\mu$ W]   | 1500 <sup>‡</sup>       | 480                     | 3.6*                   | 540               | 883.7                   |

<sup>\*</sup>Excluding circuits on FPGA.

<sup>&</sup>lt;sup>c</sup>Simulation results with Spice level 61.

FIGURE 12: Cycle of T/H block outputs: (a) full and (b) partly magnified in time.

number of bits (ENOB) and signal-to-noise plus distortion ratio (SNDR). The input signal is sine wave; the output signals are the digital codes; then these codes are converted to analog formation by an ideal DAC. Figure 15 shows the output spectrum of the ADC, which extracts an ENOB of 5.05 bits, a SNDR of 32.17 dB at an average power consumption of  $883.7~\mu W$ .

Table 2 presents the results obtained in this work in comparison to those from others. In terms of frequency, our circuit achieves the clock speed of 2 KHz, which is the highest value ever reported in organic ADC [12, 14, 18, 19]. Furthermore, other parameters, such as supply voltage, ENOB, sampling rate, and power dissipation, are very comparable to those from the others.

$<sup>^{\</sup>mathrm{a}}$ Simulated and measured results.  $^{\dagger}$ Simulation data with Spice level 1.  $^{\ddagger}$ Measured data.

<sup>&</sup>lt;sup>b</sup>Measured results.

FIGURE 13: Waveforms of outputs (Out *p*, Out *n*), control clock signal (clk\_c), and power consumption of dynamic comparator (*I*32:pwr).

Up to now, there are four reported works on ADCs, which are compared to our work as seen in Table 2. Reference [12], for example, archives highest sampling frequency of 500 Hz; [18] reduces power supply voltage to the smallest value of 3 V compared to tens of volt in others. The highest resolution is 6 bits in [14, 18], and this work, and the best linearity in [19] is expressed with DNL and INL is 0.24 and 0.42 LSB, respectively. To obtain those encouragements the circuits have to suffer from some disadvantages. For instance, the ADC in [12] consumes up to 1.5 mW, and [18] gets DNL and INL is 2.6 and 3 LSB before digital calibration on FPGA, respectively. Reference [14] contains a voltage controlled oscillator (VCO) generating the maximum frequency below 40 Hz and uses a large number of transistors due to using only P-type technology, and sampling frequency in [19] is only 4.17 Hz at 40 V power supply voltage. It is noted that the above limitations would prevent the ADCs from any application apart from [14], which could be proposed for smart chemical or temperature sensors. In terms of frequency, our circuit gets the highest clock speed of 2 KHz, which is four times higher than that of the second one. Furthermore, our ENOB is good enough while the power consumption is medium.

#### 5. Conclusions

We have utilized pentacene P-channel and fullerene N-channel TFTs to design and simulate organic integrated

FIGURE 14: Timing diagram made from SAR logic outputs.

circuits thanks to creating their valid models with the OPDK added in Cadence. The organic circuits, including logic gates, flip-flops, comparators, and analog-to-digital converters (ADCs), work properly in biopotential frequency ranges. The SAR ADC achieves 5.05-bit ENOB, 32.17 dB SNR with a power consumption of 883.7  $\mu W$  at 10 V supply voltage, and 2 KHz clock pulses. With above-mentioned results, we strongly believe that the models can help to save the time and cost in organic IC design and manufacturing.

FIGURE 15: Output spectrum.

#### **Competing Interests**

The authors have no conflict of interests associated with this paper.

#### Acknowledgments

This work has been supported by the National Foundation for Science and Technology Development (NAFOSTED) of Vietnam under Grant no. 103.99-2013.13 and University of Transport and Communications under Grant code T2016-DDT27.

#### References

- [1] H. Fan, Q. Wei, F. Qiao, and H. Yang, "A novel redundant pipelined successive approximation register ADC," *IEICE Electronics Express*, vol. 10, no. 5, Article ID 20130047, 2013.

- [2] Y. M. Greshishchev et al., "A 40 GS/s 6b ADC in 65 nm CMOS," in Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC '10), pp. 390–391, San Francisco, Calif, USA, February 2010.

- [3] R. Sekimoto, A. Shikata, K. Yoshioka, T. Kuroda, and H. Ishikuro, "A 0.5-v 5.2-fj/conversion-step full asynchronous sar adc with leakage power reduction down to 650 pw by boosted self-power gating in 40-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 11, pp. 2628–2636, 2013.

- [4] G. Dell'Erba, A. Luzio, D. Natali et al., "Organic integrated circuits for information storage based on ambipolar polymers and charge injection engineering," *Applied Physics Letters*, vol. 104, no. 15, Article ID 153303, 2014.

- [5] S. Mandal and Y. Noh, "Printed organic thin-film transistorbased integrated circuits," *Semiconductor Science and Technol*ogy, vol. 30, no. 6, Article ID 064003, 2015.

- [6] T. Sekitani and T. Someya, "Stretchable organic integrated circuits for large-area electronic skin surfaces," MRS Bulletin, vol. 37, no. 3, pp. 236–245, 2012.

- [7] A. Ciprut, A. Chelly, and A. Karsenty, "Usage and limitation of standard mobility models for TCAD simulation of nanoscaled FD-SOI MOSFETs," *Active and Passive Electronic Components*, vol. 2015, Article ID 460416, 9 pages, 2015.

- [8] N. P. Papadopoulos, A. Marsal, R. Picos, J. Puigdollers, and A. A. Hatzopoulos, "Simulation of organic inverter," *Solid-State Electronics*, vol. 68, pp. 18–21, 2012.

- [9] M. Ghasemi, M. Sam, M. H. Moaiyeri, F. Khosravi, and K. Navi, "A new SPICE model for organic molecular transistors and a novel hybrid architecture," *IEICE Electronics Express*, vol. 9, no. 10, pp. 926–931, 2012.

- [10] V. Vaidya, J. Kim, J. N. Haddock, B. Kippelen, and D. Wilson, "SPICE optimization of organic FET models using charge transport elements," *IEEE Transactions on Electron Devices*, vol. 56, no. 1, pp. 38–42, 2009.

- [11] Organic Process Design Kit, http://opdk.umn.edu.

- [12] H. Marien, M. S. J. Steyaert, E. van Veenendaal, and P. Heremans, "A fully integrated ΔΣ ADC in organic thin-film transistor technology on flexible plastic foil," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 1, pp. 276–284, 2011.

- [13] T. Zaki, F. Ante, U. Zschieschang et al., "A 3.3 v 6-bit 100 kS/s current-steering digital-to-analog converter using organic P-type thin-film transistors on glass," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 1, pp. 292–300, 2012.

- [14] D. Raiteri, P. V. Lieshout, A. V. Roermund, and E. Cantatore, "An organic VCO-based ADC for quasi-static signals achieving 1LSB INL at 6b resolution," in *Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC '13)*, pp. 108–109, IEEE, San Francisco, Calif, USA, February 2013.

- [15] M. Estrada, A. Cerdeira, J. Puigdollers et al., "Accurate modeling and parameter extraction method for organic TFTs," *Solid-State Electronics*, vol. 49, no. 6, pp. 1009–1016, 2005.

- [16] IEEE, "IEEE standard for test methods for the characterization of organic transistors and materials," IEEE Standard 1620-2008, IEEE, 2008.

- [17] D. Prutchi and M. Morris, Design and Development of Medical Electronic Instrumentation, John Wiley & Sons, Hoboken, NJ, USA, 2005.

- [18] W. Xiong, U. Zschieschang, H. Klauk, and B. Murmann, "A 3V 6b successive-approximation ADC using complementary organic thin-film transistors on glass," in *Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC '10)*, pp. 134–135, San Francisco, Calif, USA, February 2010.

- [19] S. Abdinia, M. Benwadih, R. Coppard et al., "A 4b ADC manufactured in a fully-printed organic complementary technology including resistors," in *Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC '13)*, pp. 106–107, San Francisco, Calif, USA, February 2013.

- [20] B. Murmann, "ADC Performance Survey 1997–2015," http://web.stanford.edu/~murmann/adcsurvey.html.

- [21] A. M. Abo and P. R. Gray, "A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 5, pp. 599–606, 1999.

- [22] C.-C. Liu, S.-J. Chang, G.-Y. Huang, and Y.-Z. Lin, "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 4, pp. 731–740, 2010.

Submit your manuscripts at http://www.hindawi.com

International Journal of Antennas and

Propagation